Happy Thanksgiving!

Because it is the venerated holiday, this is going to be quick!

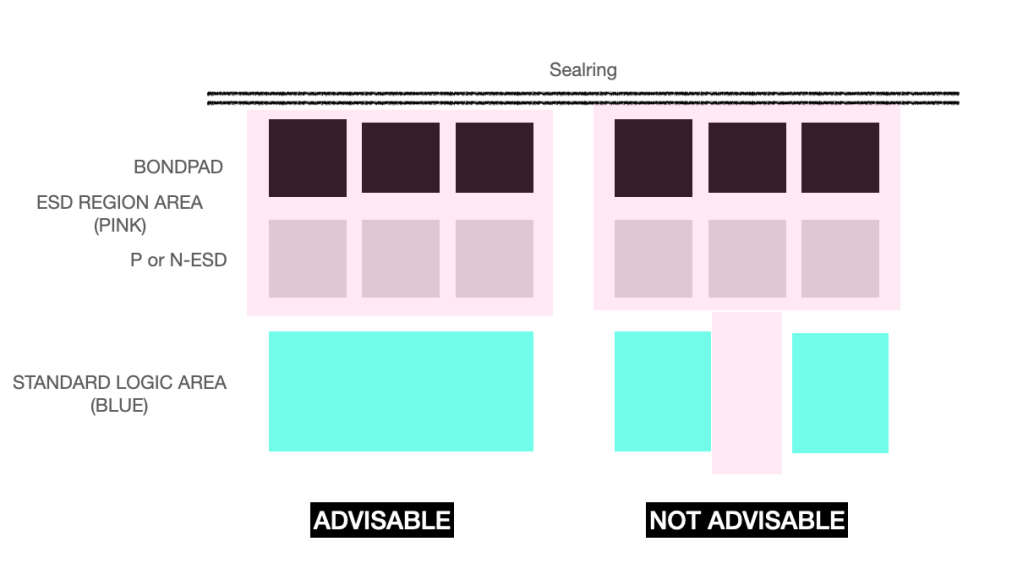

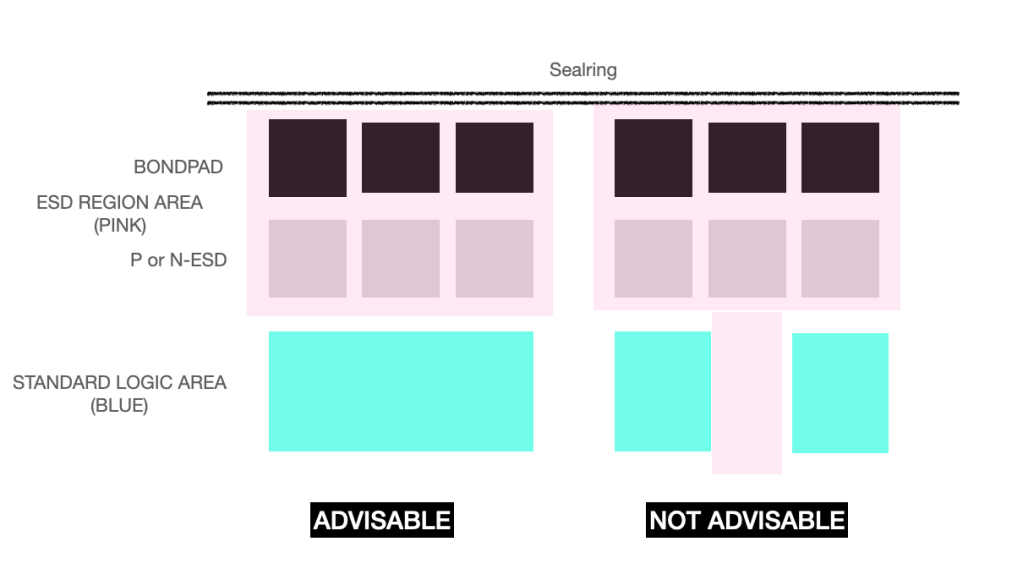

When you are planning your subcircuits, especially the mixed signal ones that involve ESD connections, please try to keep your ESD affected circuits in the ESD region and do not do like Civil War General Sherman marching to the sea and divide your quiet logic area like it’s a place to be conquered.

I think one of the reasons this occurs. is no one looks that the schematics to understand which nodes get connected to a bondpad or, possibly, a last minute circuit change is made and the only option is to break this barrier, or possibly someone chose not to change the layout that ought to be changed to make room for an ESD device in the ESD region.

Whatever the case, it may very well be that the ESD errors resulting from this aberration become a legacy that future generations of engineers have to study and wonder about to make sure it’s actually not causing 2nd order-type yield issues.

One thing to keep in mind is, whereas HV regions are pretty predictable in DRC rules, ESD gets into witchcraft and due care ought to be exercised.

Enough said

***

For those of you prone to too much alcohol indulgence over the holiday, a high dose of Vitamin B Complex during and the day after can help curb the hangover effects on your poor liver.

Feel free to Like, Share, Follow, and Comment

CKY

***

Copyright © 2023 Challen Yee / ICLayout.blog Some Rights Reserved

Leave a comment