I ran across this situation when I was drawing the high speed read data path for a special memory and capacitance of a shared data bus became an issue. On certain schemes, there may be multiple transmission gates (XFRs) connected to the same bus line, hence, the cumulative drain capacitance caused some concern on the SIMs.

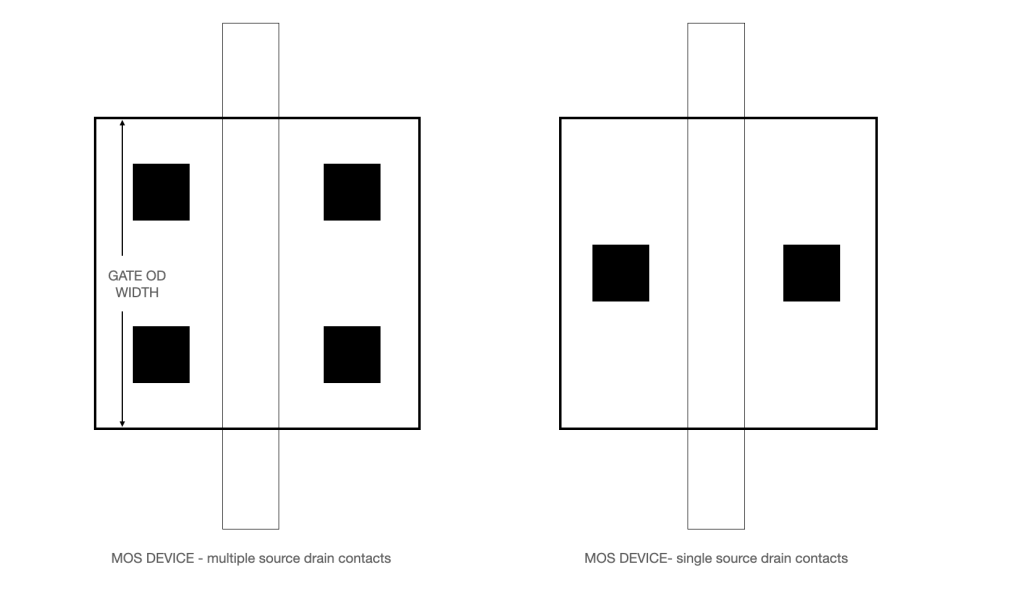

The consideration is if you need to reduce capacitance, and the metal bus is already drawn to its minimum width and optimal spacing, and decoupled from other noise or other voltage nets. In order to further decrease capacitance, you may consider reducing the number of contacts on the source and drain of the XFRs.

You may see fit to reduce the number of contacts, since every contact within themselves adds capacitance.

Of course, you need to consider the DRC rules, however, it is recommended the reduction in capacitance needs to be weighed vs added resistance of decreasing the number of contacts.

For an eye exercise, you can focus on your thumb moving it near and to the fullest extent of your arm and around from periphery to periphery to refresh some blood circulation to your eyes.

Feel free to Like, Share, Follow, and Comment

CKY

***

Copyright © 2023 Challen Yee / ICLayout.blog Some Rights Reserved

Leave a reply to ark Cancel reply