When to check WELL TO WELL DRC

This is part of your “top down” methodology or “Think like a project leader” tip. This is especially true when working with mixed signal and fitting a control subblocks into something immovable like an arrayed memory bank with its pitch circuitry in place. That’s certainly one of a thousand examples.

It is expected that every subcell that is completed and “delivered” to the project lead is clean in every respect and from a level high enough to catch every error the new block may introduce to the top level of the design. The exception being, if there is a collaboration with the lead designer and/or team members noting any errors with the new layout.

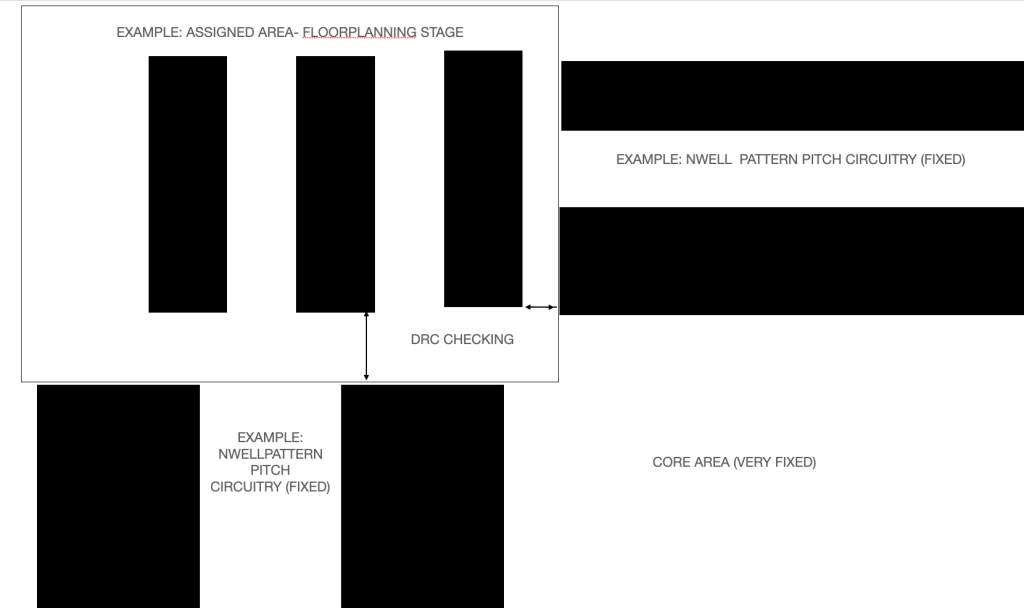

EXAMPLE OF NWELL PATTERNS IN A MEMORY BLOCK

In your initial floor plan, it is a not uncommon oversight to neglect the border conditions or at least some obscure border condition. When creating sub blocks beware not to overlook an NWELL spacing problem. This situation, for instance, may occur when fitting a row or column control subblock or other control circuitry into the “hole” created by column and rows pitch circuitry.

If possible, you want to not share an NWELL with a pitch block, even if it is the same potential. It helps later to manage changes, to avoid introducing noise between blocks, or to maintain the symmetry of the pitch layout.

You want to also ensure the NWELL or other WELL spacings meet the most conservative spacing rule that is active in your project, not only the minimum rule. This may include running every rundeck (i.e. DRC, ERC, Mixed-Signal checks) to catch a valid and exceptional or otherwise surprise error. If you need to assign your power rails with the correct LVS pins/text before running, do it.

In the memory example (seen in the illustration above), you may, as the draftsman assigned the control block as in the example above, make sure that the pitch areas are DRC clean AND that any necessary dummy structures or redundancies are in place for matching. Those will eat up a lot of space if they are not implemented already.

It pays to take the relatively short time to run the DRCs and then, if clean, proceed with more detailed aspects of your floor planning or routing, rather than, when you are running LVS, discovering you need to move a bunch of nice layout to fix the NWELL /DNWELL spacing error from hell.

***

One of the most profound pieces advice I ever received from a circuit engineer: “Eat your meals on a regular schedule.“

Feel free to Like, Share, Follow, and Comment

CKY

***

Copyright © 2023 Challen Yee / ICLayout.blog Some Rights Reserved

Leave a reply to ICL WW-23.02 Weekly Wrap for 11-13 thru 11-17-23 – IC Layout Cancel reply